# Efficient Approaches to Design Full Adder Using Domino Logic Technique

# M. Surekha<sup>1</sup>, V. HariKrishna<sup>2</sup>, B. MadhuSudhan Reddy<sup>3</sup>, G.Tejaswini<sup>4</sup>, I.Rajasekhar<sup>5</sup>, K.Divya<sup>6</sup>

<sup>1</sup>Assistant Professor – Electronics and Communication Engineering, PBR VITS, Kavali. <sup>2,3,4,5,6</sup> UG - Electronics and Communication Engineering, PBR VITS, Kavali Corresponding Author Orcid ID : 0009-0004-9046-6513

#### ABSTRACT

Static CMOS and Domino CMOS Circuits are significantly used in high performance VLSI system. Designing a circuit with low power, high speed performance is one of the challenging aspects. In modern VLSI systems area efficient devices are utmost popular because most of the devices are becoming portable. This paper proposes One- bit full adder circuit is designed using CMOS based on mirror logic and Domino CMOS also designed based on same logic with LTSPICE at 180nm technology with 1.8V supply. This method provides better power and delay.

Key words: CMOS Full Adder, Domino Logic Full Adder and Mirror Logic.

#### 1. Introduction

In the fast-growing VLSI industry, transistor density is increasing with rapid rate day-by-day .According to Moore's law transistor density will get doubled itself after every eighteen months. As the number of transistor will increase, correspondingly area, delay and power consumption of the device will also increase .So ,a technology is required by which the area can be reduced and increase the performance of the device. From the past few decades CMOS technology [1] is being used for designing the chips in semiconductor Industry ,but as the number of transistor are increasing ,area of the device and delay both are increasing .So it requires to switch to a technology ,which uses lesser area and smaller delay. Hence, the domino logic is used for designing the one-bit full adder and compared the various performance parameter like area, delay, and power consumption in both technology

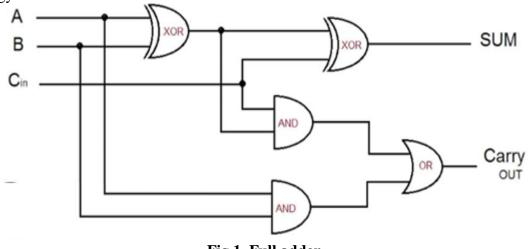

Fig 1. Full adder

#### 2. Existing system

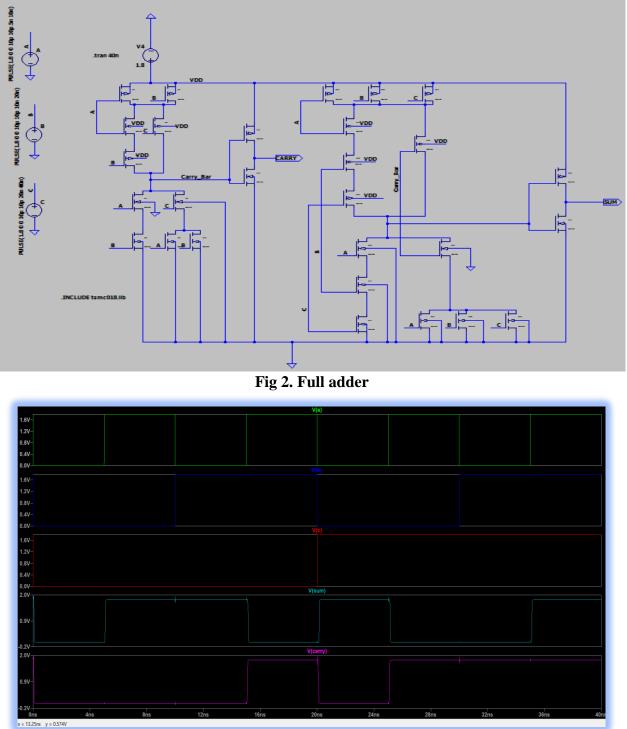

CMOS (complementary metal oxide semiconductor). Static CMOS circuits uses complementary NMOS pulldown and PMOS pull-up networks to implement logic gates or logic functions in integrated circuits. It requires 2N transistors to design a N input logic function. The static power loss is high When the input is '0' then P-MOS will be on and it will charge the output node to vdd. When the input is '1' then N-MOS will be on and the charge stored at the output node get a conducting path

between output node and ground. Here we used 28- transistor [2] among them 14 P-MOS and 14 N-MOS transistors are used to develop the Full-Adder in C-MOS technology. The power of the full-adder is -9.8135uw

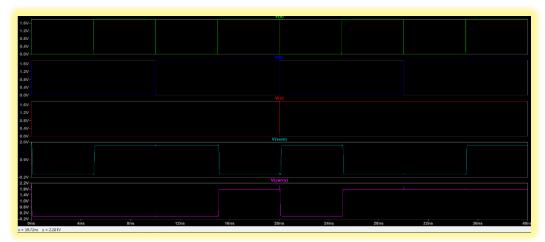

Fig 3. Simulation Result of FA CMOS Logic

## 3. Dynamic CMOS

Dynamic is an alternative logic style .Which is better than static mode. Its consists of faster switching speeds, no static power consumption ,non-ratioed logic, Full swing voltage levels and less number of transistors. To design an N Input logic function it requires N+2 transistors versus 2N transistors in standard CMOS Logic. High speed is the distinct specification of this Logic It consists of two phases

Website: ijetms.in Issue: 2 Volume No.7 March - April – 2023 DOI:10.46647/ijetms.2023.v07i02.033 ISSN: 2581-4621

pre-charge and evaluation phase. When Clock=0, circuit enters into precharge phase and the output is connected to vdd, when the clock=1,circuit enters into evaluation phase and the output is connected to gnd through NMOS network.

#### **Dynamic CMOS Limitations**

It consists of problems like capacitive coupling, charge leakage and charge sharing. Limitation in cascading several stages which is overcome by domino logic. Some excess power is consumed because the circuit has to be precharged after every evaluation. The pull down network takes longer time to evaluate its output. If clock arrives earlier.

#### 4. Proposed system: Domino CMOS logic

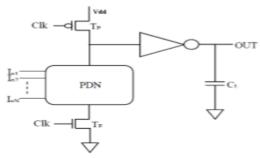

#### Fig 4. Domino Logic

Domino logic family finds a wide variety of applications. The less transistor count compared to CMOS. The high speed of operation such as microprocessors, dynamic memory, etc. It's an evolution in CMOS-based dynamic logic technique. An inverter is used to avoid the cascading problem in dynamic logic. Requires less area. Here we used the 1.8v and 22 transistors among them 2-transistors are keeper transistors. The keeper transistors are used to overcome the noise. 6-PMOS transistors and 14-NMOS transistors. We designed the full adder by using the mirror logic Properties of Domino CMOS

• Since each dynamic gate has a static inverter, only non-inverting logic can be implemented.

• Very high speeds can be achieved: only a rising edge delay exists, while tpHL equals zero.

• The inverter can be sized to match the fan-out, which is already much smaller than in the complimentary static CMOS case, as only a single gate capacitance has to be accounted for per fan-out gate Properties of Domino CMOS

• Since each dynamic gate has a static inverter, only non-inverting logic can be implemented.

• Very high speeds can be achieved: only a rising edge delay exists, while tpHL equals zero.

• The inverter can be sized to match the fan-out, which is already much smaller than in the complimentary static CMOS case, as only a single gate capacitance has to be accounted for per fan-out gate Properties of Domino CMOS

• Since each dynamic gate has a static inverter, only non-inverting logic can be implemented.

• Very high speeds can be achieved: only a rising edge delay exists, while tpHL equals zero.

• The inverter can be sized to match the fan-out, which is already much smaller than in the complimentary static CMOS case, as only a single gate capacitance has to be accounted for per fan-out gate

Website: ijetms.in Issue: 2 Volume No.7 March - April - 2023 DOI:10.46647/ijetms.2023.v07i02.033 ISSN: 2581-4621

#### **1 Bit Full adder using Mirror logic**

- Implementation using (inversion and duality) properties gives logic

- Any expression that satisfy inversion property also exhibits duality

- principle i.e  $AND \leftrightarrow OR$ Cout = AB + Cin(A + B)cout = (A + B).(Cin + AB)It's duality is = Acin + Bcin + AAB + ABB= Acin + Bcin + AB + AB= Acin + Bcin + ABCout = AB + Cin(A + B)i.e  $Cout = AB + Cin(A + B) \Leftrightarrow cout = (A + B).(Cin + AB)$  $Sum = ABCin + \overline{Cout}(A + B + Cin)$  $sum = (A + B + Cin)(\overline{Cout} + ABCin)$ It's dual is  $= A\overline{Cout} + AABCin + B\overline{Cout} + ABBCin + Cin\overline{Cout} + ABCinCin$  $= A\overline{Cout} + B\overline{Cout} + Cin\overline{Cout} + ABCin$  $sum = \overline{Cout}(A + B + Cin) + ABCin$ i.e  $sum = ABCin + \overline{Cout}(A + B + Cin) \Leftrightarrow (A + B + Cin)(\overline{Cout} + ABCin)$ Inversion

$$Cout = AB + ACin + BCin \Leftrightarrow \overline{Cout} = \overline{AB} + \overline{BCin} + \overline{A} \overline{Cin}$$

$Sum = ABCin + \overline{Cout}(A + B + Cin) \Leftrightarrow \overline{sum} = \overline{ABCin} + Cout(\overline{A} + \overline{B} + \overline{Cin})$

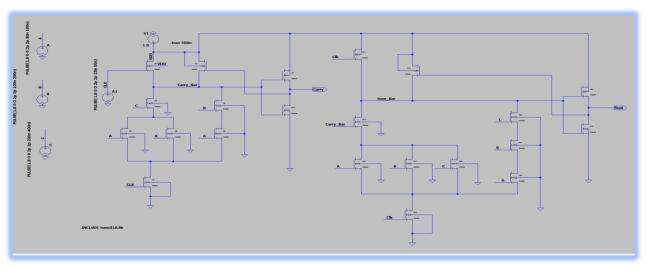

Fig 5. 1-Bit Full Adder (Static CMOS)

#### Fig 6. Simulation Result of Static CMOS

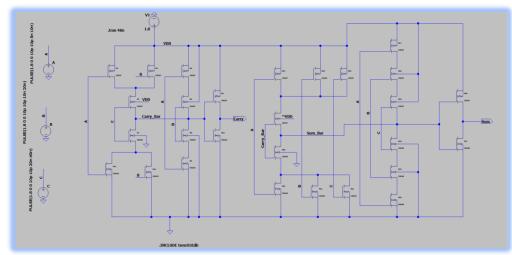

Fig 7. 1-Bit Full Adder (Domino CMOS)

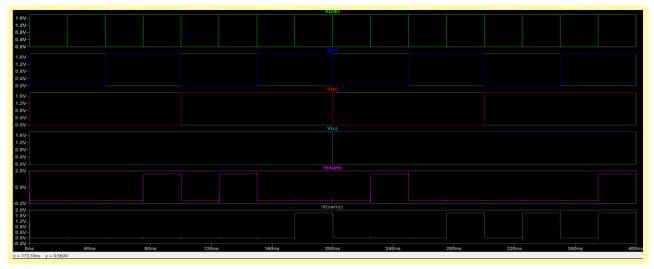

Fig 8. Simulation Result of Domino CMOS

#### CONCLUSION

In this paper designing of full adder circuit using the CMOS logic and Domino logic has been done. We used LT SPICE software, 180nm technology for analyzing the full adder circuit. It was found that Domino logic gives us very accurate results with less number of transistors and minimum delay as compare to the CMOS design logic. There are almost no glitches in Domino logic transient analysis. Further there is a decrease in chip area by 28.5% and delay by 47.37% in Domino logic as compared to CMOS logic.

## References

[1] C. Chiang, J.-Y. Jiang, H.-W. Hung, C.-Y. Wu, G.S. Chen, and J. Lee, (Feb. 2015).  $-4 \times 25$  Gb/s transceiver with optical front-end for 100 Gb system in 65 nm CMOS technology, IEEE J. Solid-State Circuits, vol. 50, no. 2, pp. 573–585,

[2] H. Chu, W. Bae, G.-S. Jeong, J. Joo, G. Kim, and D.-K. Jeong,(Nov. 2014)—A 26.5 Gb/s optical receiver with all-digital clock and data recovery in 65 nm CMOS process, in Proc. Asian Solid-State Circuits Conf., , pp. 101–104

[3] N.Weste and K. Eshragian, Principles of CMOS VLSI Design: A Systems Perspective, Reading, MA: Addison Wesley, 1988, pp 231-237.

#### **International Journal of Engineering Technology and Management Sciences**

Website: ijetms.in Issue: 2 Volume No.7 March - April – 2023 DOI:10.46647/ijetms.2023.v07i02.033 ISSN: 2581-4621

[4] S. Kao, F.-T. Chen, Y.-H. Hsu, and J.-M. Wu, (Mar. 2014) —20-Gb/s CMOS EA/MZ modulator driver with intrinsic parasitic feedback network, IEEE Trans. Very Large-Scale Integration. (VLSI) Syst., vol. 22, no. 3, pp. 475–483,

[5]Adaikalam, S.Manikandan, V.Rajamani, —A modified priority-based multischeduler (pbms) for optical network Advances in Intelligent systems and computing, PP 665-667, VOL NO:324, 2015.

[6] V. Krishnamoorthy et al., (Dec. 2006) —Computer systems based on silicon photonic interconnects, Proc. IEEE, vol. 97, no. 7, pp. 1337–1361, Jul. 2009.B. Analui, D. Guckenberger, D. Kucharski, and A. Narasimha, —A fully integrated 20-Gb/s optoelectronic transceiver implemented in a standard 0.13-μm CMOS SOI technology, IEEE Solid -State Circuits, vol. 41, no. 12, pp. 2945–2955.

[7] M. Amitha and Deepa, "Comparison between CMOS full adder and PTL full adder", IOP Conference Series: Materials Science and Engineering (ICFEST 2020), IOP Publishing, 2020.

[8] Kothapalli Srujana, Kummari Shivani, Kuruva Thirumalesh and Lakku Yashaswi, "Optimizing Conventional Full Adder Design for Power-Efficient Applications, Journal of VLSI and Computer Systems, vol. 1, no. 1, pp. 1-5, 2020.

[9] Mehedi Hasan, Md. Jobayer Hossein, Mainul Hossain, Hasan U. Zaman, Sharnali Islam, "Design of a Scalable Low-Power 1-Bit Hybrid Full Adder for Fast Computation", IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 67, no. 8, pp. 1464-1468, 2020.

[10] A. Benjamin Franklin and T. Sasilatha, "Design and Analysis of Low Power Full Adder for Portable and Wearable Applications", International Journal of Recent Technology and Engineering, vol. 7, no. 5S3, pp. 295-299, 2019.

[11] Zhiyu Liu, Volkan Kursun, "PMOS-Only Sleep Switch Dual-Threshold Voltage Domino Logic in Sub-65-nm CMOSTechnologies", IEEE Trans. Very Large-Scale Integration (VLSI) Systems,vol. 15, no. 12, DEC. 2007.

[12] Zhiyu Liu, Volkan Kursun, "Leakage Power Characteristics of Dynamic Circuits in Nanometer CMOS Technologies", IEEE Trans. Circuits and Systems-II, vol. 53, no. 8, 2006.

[13] Sharroush, S. M., Abdalla, Y. S., Dessouki, A. A. El-Badawy, E. S. A., "A novel low-power and high-speed dynamic CMOS logic circuit technique" IEEE confrenceIn Radio Science Conference, National pp. 1-8, 2009.

[14] L. Ding and P. Mazumder, "On Circuit Techniques to Improve Noise Immunity of CMOS Dynamic Logic,"IEEE Transactions on Circuits and Systems, 2004.

[15] Karuppusamy, P. " Design and Analysis Of Low-Power, HighSpeed Baugh Wooley Multi-Plier" Journal of Electronics 1, no. 02 (2019): 60-70.

[16] Kamlesh Kukreti, Rais Ahmad, Anzar Ahmad, "Design and Implementation A Low Power Rail-To-Rail Preamplifier", Universal Review ,2018.