Website: ijetms.in Issue: 5 Volume No.7 September - October – 2023 DOI:10.46647/ijetms.2023.v07i05.065 ISSN: 2581-4621

# A Novel Implementation of QPSK Modulator on FPGA

**B** Reshma Parveen

Research Scholar -Electronics and Communication Engineering, YV University, Kadapa, Andhra Pradesh

## ABSTRACT

QPSK is one of the digital modulation techniques in communication system that has wide applications in the field of wireless, satellite communication, Bluetooth, OFDM etc. The Conventional QPSK modulators designs are generally based on IQ approach. In these modulators multipliers are used to separate the modulating signal into the in-phase and quadrature phase which increases the hardware complexity. The objective of this work is to implement the digital QPSK modulator with conventional and another approach of digitization. In this approach a digitized carrier wave is generated and QPSK phase shifting is provided by 4:1 multiplexer according to the data bits. The implementations of both the designs are done on Spartan 3E Xilinx FPGA through the verilog hardware description language. The QPSK modulator based on the Digitized approach is simpler in terms of hardware circuitry.

Keywords— Quadrature Phase Shift Keying (QPSK); Deterministic Random Bit Generator (DRBG); Verilog; Look up table (LUT); FPGA; Serial in Parallel out (SIPO).

## 1. Introduction :

Modulation is phenomena in which characteristic like amplitude, phase and frequency of a high frequency carrier wave is changed accordingly low frequency modulating wave. Modulation is required to minimize the noise in signal and to separate the signal from different transmitters. Generally, Modulation can be done by two ways the analog and digital modulation.Digital modulation provides more information capacity, greater noise immunity, robustness to channel impairments, higher data security, better quality communication, compatibility with digital data service.Faster system availability and easier multiplexing of various forms of information like voice, data and video etc.

# 2. Experimental Methods or Methodology

Multiplier 2

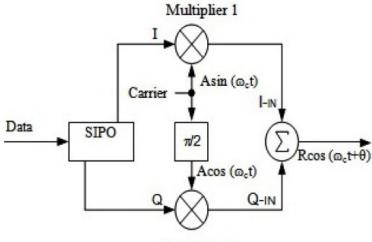

Fig 1. Existing System

In the existing system, The circuit is based on IQ Modulation. As the symbol contains two bits, so one bit modulates in phase-carrier and second bit will modulate the quadrature phase-carrier. The bits are named as the I and Q respectively, and are transmitted to the modulator via a Serial-In-Parallel-Out (SIPO) shift register. SIPO accepts the input from the data and converts it to the parallel data. The existing system uses two multipliers and the mixer as well so that the circuit area increase and the cost also increase. To avoid this we are using the proposed system.

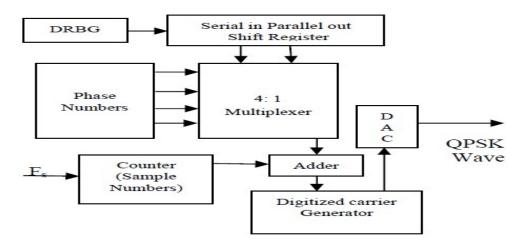

## Fig 2. Proposed System

The new approach is proposed for QPSK modulator. In this method the QPSK is generated on the digital platform by means of digitized carrier wave generator. The Proposed circuit does not use the multipliers and mixers but the conventional IQ modulator uses two multipliers, so the proposed circuit minimizes the circuit area as well as cost. We are also adding the parallel processing registers to the proposed system to increase the throughput and the speed.

## 3. Results and Discussion

# 3.1 Synthesis Results:

3.1.1 Existing System:

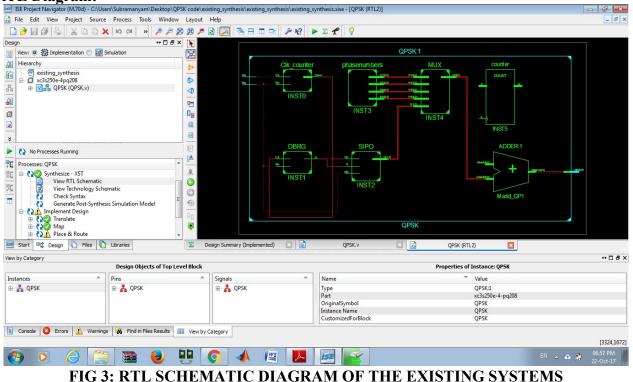

## **RTL Diagram**:

International Journal of Engineering Technology and Management Sciences

Website: ijetms.in Issue: 5 Volume No.7 September - October - 2023 DOI:10.46647/ijetms.2023.v07i05.065 ISSN: 2581-4621

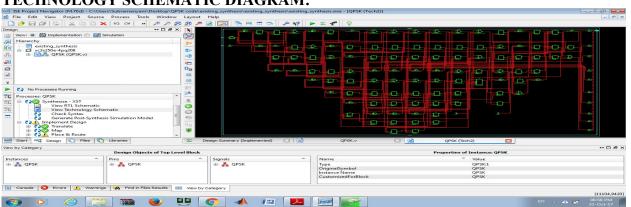

## **TECHNOLOGY SCHEMATIC DIAGRAM:**

### FIG 4: TECHNOLOGY SCHEMATIC DIGRAM OF THE EXISTING SYSTEM

The technology schematic diagram contains the LUTs. Each of the LUT contains a specific function. If the number of Look Up Tables increases then the size of the IC will also increase.

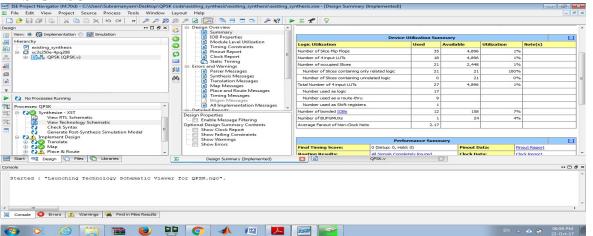

## **DESIGN SUMMARY:**

# Fig 5: DESIGN SUMMARY OF THE EXISTING SYSTEM

The design summary shows the number of look up tables, number of flip flops and the number of I/O bonds used in the design.

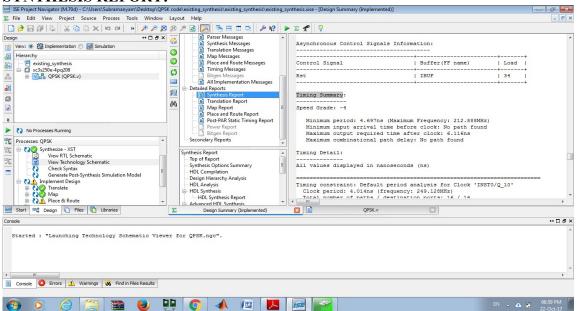

# SYNTHESIS REPORT:

# Fig 6: SYNTHESIS REPORT OF THE EXISTING SYSTEM

Website: ijetms.in Issue: 5 Volume No.7 September - October - 2023 DOI:10.46647/ijetms.2023.v07i05.065 ISSN: 2581-4621

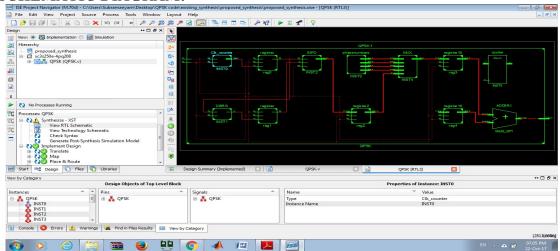

## 3.1.2 PROPOSED SYSTEM: RTL SCHEMATIC DIAGRAM:

# Fig 7: RTL SCHEMATIC DIAGRAM OF THE PROPSOED SYSTEM SCHEMATIC DIAGRAM:

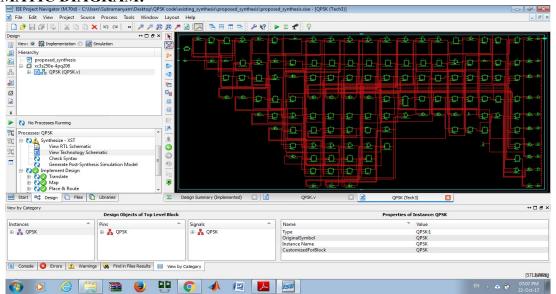

# FIG 8: SCHEMATIC DIAGRAM OF THE PROPOSED SYSTEM DESIGN SUMMARY:

| n +□6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          | Design Overview                                                       | Design Goal:               | Balanced                  |                                         | Routing Results: | Al Cionale  | Completely Routes   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------|----------------------------|---------------------------|-----------------------------------------|------------------|-------------|---------------------|--|

| View:  Ø Implementation  Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | × 🕜                      | Summary                                                               | Design Strategy:           | Xlinx Default (unlocked)  | Timing Constraints: Final Timing Score: |                  |             | All Constraints Met |  |

| Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 0                      | IOB Properties                                                        | Environment:               | System Settings           |                                         |                  |             |                     |  |

| Hielarchy Figure 2 - 20 - 20 - 20 - 20 - 20 - 20 - 20 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                        | Module Level Utilization Timing Constraints Pinout Report Cock Report | Device Utilization Summary |                           |                                         |                  |             |                     |  |

| WINN (QPSK.V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10.00                    |                                                                       | Logic Utilization          | bence                     | Used                                    | Available        | Utilization | Note(s)             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                        | Errors and Warnings                                                   | Number of Sice Fin Flor    | w                         | 52                                      | 4,896            | 1%          | note(a)             |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                        |                                                                       | Number of 4 input LUTs     | ~                         | 18                                      | 4,896            | 1%          |                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (A)                      | Translation Messages                                                  | Number of occupied Sig     | 20                        | 38                                      | 2,448            | 196         |                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8                        | Map Messages Place and Route Messages                                 |                            | aining only related logic | 38                                      | 2,110            | 100%        |                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          | Flace and Route Messages Timing Messages                              | Number of Slices con       |                           | 0                                       | 38               | 0%          |                     |  |

| Running                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          | - 🛄 Bitgen Messages                                                   | Total Number of 4 input    |                           | 34                                      | 4,896            | 1%          |                     |  |

| Processes: QPSK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ^                        | All Implementation Messages Design Properties                         | Number used as logic       |                           | 17                                      |                  |             |                     |  |

| Check Syntax<br>Generate Post-Synthesis Simulation Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |                                                                       | Number used as a ro        | ute-thru                  | 16                                      |                  |             |                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          | Optional Design Summary Contents                                      | Number used as Shift       | registers                 | 1                                       |                  |             |                     |  |

| Constant  Constant |                          | Show Clock Report                                                     | Number of bonded IOB       | 1                         | 12                                      | 158              | 7%          |                     |  |

| B C Place & Route II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Show Failing Constraints | Number of BUFGMUXs                                                    |                            | 1                         | 24                                      | 4%               |             |                     |  |

| Generate Programming File Configure Target Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          | Show Warnings                                                         | Average Fanout of Non      | Clock Nets                | 2.03                                    |                  |             |                     |  |

| Configure Target Device Analyze Design Using ChipScope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                        |                                                                       |                            |                           |                                         |                  |             |                     |  |

| Start C Design C Files C Libraries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | x                        | Design Summary (Implemented)                                          |                            | QPSK.v                    | 6                                       | x]               |             |                     |  |

| ole                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                        |                                                                       |                            |                           |                                         |                  |             |                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |                                                                       |                            |                           |                                         |                  |             |                     |  |

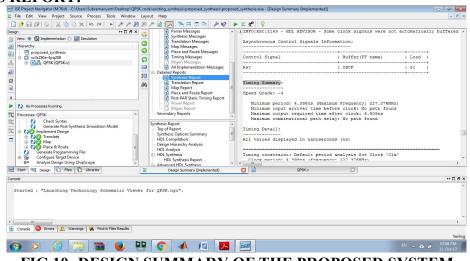

FIG 9: DESIGN SUMMARY OF THE PROPOSED SYSTEM

International Journal of Engineering Technology and Management Sciences

Website: ijetms.in Issue: 5 Volume No.7 September - October - 2023 DOI:10.46647/ijetms.2023.v07i05.065 ISSN: 2581-4621

#### **SYNTHESIS REPORT:**

FIG 10: DESIGN SUMMARY OF THE PROPOSED SYSTEM

# **3.3 SIMULATION RESULTS: 3.3.1 EXISITING SYSTEM:**

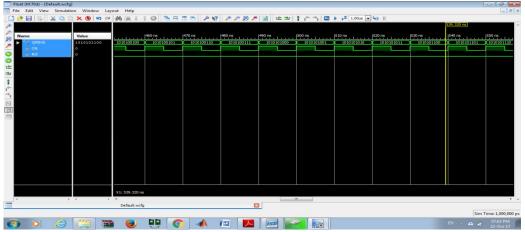

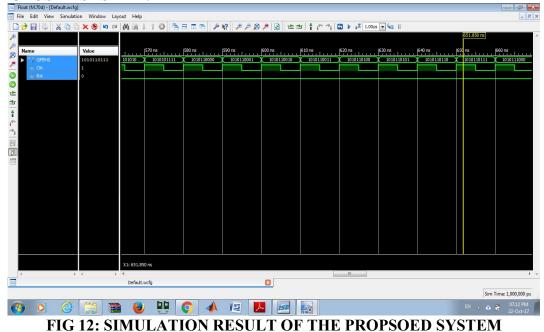

FIG 11: SIMULATION RESULT OF THE EXISTING SYSTEM 3.3.2 PROPOSED SYSTEM:

# 4. CONCLUSION:

This project presents implementation of the IQ based QPSK Modulator and the proposed digitized QPSK Modulator using Spartan 3E starter Xilinx Board synthesis. Design and implementation as well as for the development of sophisticated digital systems by using Verilog hardware description language.

In this project it is tried to achieve a design for QPSK modulation which will give the same result by minimizing its size or area as well. The reduced delay of the design will reduce the power consumption. The proposed block system, we were used the parallel processing technique to the existing system that will help to increase speed of operation of the design. It means proposed block diagram try to improve all the three main factors power, area, hardware which are taken into consideration for any system design.

### **FUTURE SCOPE:**

In future, we will use the parallel prefix adder in place of the normal adder and also use QCA technology in the design of multipliers to reduce the delay and the area reduction.

### 5. REFERENCES

- 1. T. Kazar, M.Kulin and M. Hadzialic "Design and Implementation of SDR Based QPSK Modulator on FPGA," 36th International Conference on Information and Communication Technology Electronics and Microelectronics (MIPRO) 2013.

- 2. S. O. Popescu, A.S. Gontean and D.Ianchis "QPSK Modulator on FPGA," IEEE 9<sup>th</sup> International Symposium on Intelligent Systems and Informatics, September 8-10, 2011, Subotica, Serbia, 359\_364, SIS42011.

- 3. K. Anitha, Umeshraddy and B.K. Sujatha "FPGA Implementation of High throughput Digital QPSK Modulator using Verilog HDL," International Journal of Advanced Computer Research Volume 4, Number 1, Issue-14 March 2014.

- 4. K.A. Monapara and S.B. Parmar "Design and Implementation of QPSK Modulator using Digital Subcarrier," Journal of Information, Knowledge and Research in Electronics and Communication Engineering, ISSN: 0975-6779, Nov. 11 Oct. 12, Volume 02, Issue 01 pp 394-398.

- 5. K. Mounica, S.Mohan Das and P. Uday Kumar "A Verilog Design in FPGA Implementation Of QPSK Digital Modulator," International Journal of Engineering Science and Research Technology, July 2013 1904-1909.

- A.M. Moubark, Md. Alauddin, HilmiSanusi and Sawal Md.Ali "FPGA Implementation of Low Power digital QPSK Modulator using Verilog HDL," Journal of Applied Sciences (JAS - 2013) Vol. 13, Issue 3, pp.385-392, 2013.

- 7. Preksha R. Kolankar and Swati V. Sakhare "FPGA Implementation of QPSK Modulator by using Hardware Co-Simulation,"International Journal of Engineering Research and Development Volume 10, Issue 4 April 2014 PP. 86-93.

- 8. Prashant D. Thombare and Ameed M. Shah "QPSK Modulator on FPGA using 64 values ROM," International Journal of Computer Science and Information Technologies, Vol. 5131, 2014, 3403-3406.